What we do

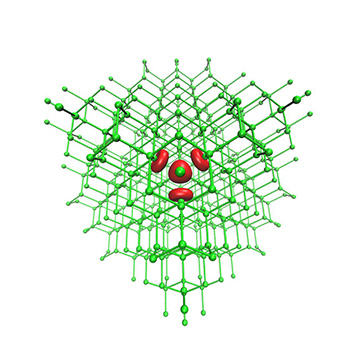

The Nanoelectronic Devices Computational Group research focuses on the Simulation and Modelling of Semiconductor Devices. The group research interests have recently expanded to the fabrication and characterisation of semiconductor device structures based on novel materials such as cubic SiC and cubic BAs.

Our main objectives are to:

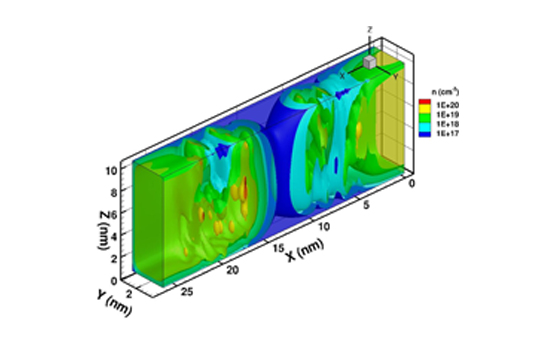

- Carry out advanced simulations and modelling of semiconductor devices

- Employ 2D real space semiclassical and quantum transport simulation techniques for microelectronics and nanoelectronics planar devices

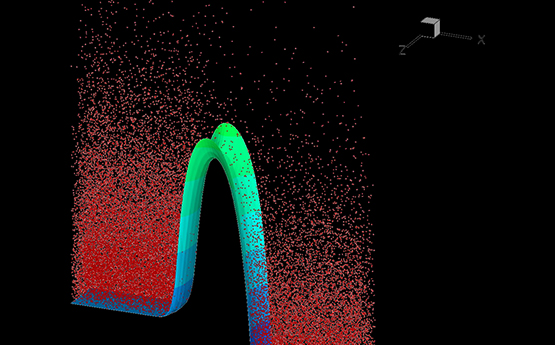

- Employ and develop 3D real space classical, semiclassical and quantum transport simulation techniques for nanoelectronics planar and non-planar devices

- Offer prestigious postgraduate research opportunities through research at the cutting edge development of nanoelectronics

Our research interests include:

- Si and III-V FinFETs

- Si Nanowires

- Si and III-V MOSFETs including thin-body architectures

- GaN HEMTs